# Reconfigurable Computer with Cycle-by-Cycle Reconfiguration and Execution Aimed to be a General-Purpose Computer

毎サイクルの再構成を可能にすることにより汎用性を目指した再構成型コンピュータ

Tetsuo Hironaka Kazuya Tanigawa Akira Kojima(Hiroshima City University) 弘中 哲夫 谷川 一哉 児島 彰 (広島市立大学)

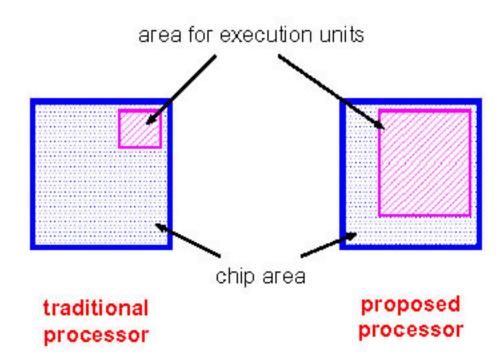

(a) Goal 1: Achieve greater performance per chip area.

#### - Goal 1 -

To achieve one to two orders of magnitude greater performance per chip area by using a reconfigurable hardware.

Super scalar processors and VLIW processors are the current main stream on exploiting instruction level parallelism. The performance of these processors depends on the number of executable instructions in parallel at its execution units. But the chip area occupied by the execution units is small, compared to the rest of the chip area occupied by its control circuits that do not contribute to the performance. From this reason, these processors end up with low performance per chip area and high power consumption per performance. A reconfigurable processor architecture, with a potential to improve performance per chip area drastically, is effective to satisfy the intense demands for both low power consumption and high performance.

#### - Goal 2 -

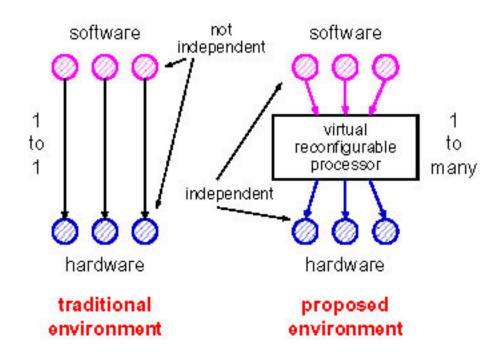

Introducing a programming model based on a virtual reconfigurable processor to develop a software environment for sharing software properties.

In the most reconfigurable architectures developed until today, the software for one reconfigurable processor deeply depends on it, so developing software and hardware independently was impossible. In the traditional processor architecture, this feature has been realized by providing a hierarchy between software and hardware. This means, it is impossible for a reconfigurable architecture to be used as a next generation general-purpose architecture, without providing a hierarchy between software and hardware. So, we have developed a reconfigurable architecture based on a programming model with the ability to provide a hierarchy between software and hardware.

Now, we are designing the prototype machine to realize the above two goals

(b) Goal 2: Develop a software environment for sharing software properties between different hardware.

## -目標 1-

再構成型ハードウェアにより処理に合わせて必要な演算器を必要数構成できるようにすることで、単位面積 あたりの演算処理能力を数十~数百倍向上させる.

現在、命令レベル並列性を利用したプロセッサとしてスーパスカラや VLIW が主流である。これらの性能は実行ユニットで並列実行可能な命令の個数に依存する。しかし、プロセッサのチップ面積のうち実行ユニットが占めるチップ面積の割合は小さく、残りの大部分の面積は演算に直接関係無い制御回路によって占められている。そのため、チップ面積当りの演算性能が低く、かつ、演算性能に対する消費電力が大きなものになっている。したがって、現在厳しく要求されている低消費電力化と高性能化を同時に満たすには、チップ面積あたりの演算性能を大幅に向上させる可能性をもつ再構成型アーキテクチャが有効である。

### -目標 2-

ソフトウェア資産を共有できる環境を構築するため、仮 想化された再構成型プロセッサを使用したプログラミ ングモデルを実現する.

これまで研究されてきた再構成型プロセッサにおいて、 特定の再構成型プロセッサ用のプログラムはそれ以外の プロセッサでの動作を保証できず、ソフトウェアとハード ウェアそれぞれ独自の開発が不可能であった。それに対 し、従来のアーキテクチャではソフトウェアとハードウェ アの階層化によってそれらを実現していた。つまり、ソフトウェアとハードウェアの階層化ができないことが、再構 成型アーキテクチャを次世代の汎用アーキテクチャとして 使用する上で大きな障害となっている。そこで、我々はソフトウェアとハードウェアの階層化が可能なプログラミン グモデルを持つ再構成型アーキテクチャの研究開発を行っ ている。

現在、上記2目標を実現する試作機を設計中